August 1998

# 100331

# Low Power Triple D Flip-Flop

### **General Description**

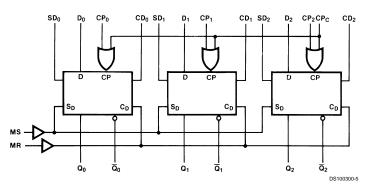

The 100331 contains three D-type, edge-triggered master/slave flip-flops with true and complement outputs, a Common Clock (CP<sub>C</sub>), and Master Set (MS) and Master Reset (MR) inputs. Each flip-flop has individual Clock (CP<sub>n</sub>), Direct Set (SD<sub>n</sub>) and Direct Clear (CD<sub>n</sub>) inputs. Data enters a master when both CP<sub>n</sub> and CP<sub>C</sub> are LOW and transfers to a slave when CP<sub>n</sub> or CP<sub>C</sub> (or both) go HIGH. The Master Set, Master Reset and individual CD<sub>n</sub> and SD<sub>n</sub> inputs override the Clock inputs. All inputs have 50 k $\Omega$  pull-down resistors.

#### **Features**

- 35% power reduction of the 100131

- 2000V ESD protection

- Pin/function compatible with 100131

- Voltage compensated operating range = -4.2V to -5.7V

- Available to industrial grade temperature range

- Available to Standard Microcircuit Drawing (SMD) 5962-9153601

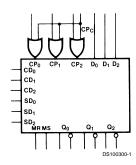

#### **Logic Symbol**

| Pin Names                         | Description                    |

|-----------------------------------|--------------------------------|

| CP <sub>0</sub> -CP <sub>2</sub>  | Individual Clock Inputs        |

| CP <sub>C</sub>                   | Common Clock Input             |

| D <sub>0</sub> -D <sub>2</sub>    | Data Inputs                    |

| CD <sub>0</sub> -CD <sub>2</sub>  | Individual Direct Clear Inputs |

| SD <sub>n</sub>                   | Individual Direct Set Inputs   |

| MR                                | Master Reset Input             |

| MS                                | Master Set Input               |

| Q <sub>0</sub> -Q <sub>2</sub>    | Data Outputs                   |

| $\overline{Q}_0 - \overline{Q}_2$ | Complementary Data Outputs     |

# **Connection Diagrams**

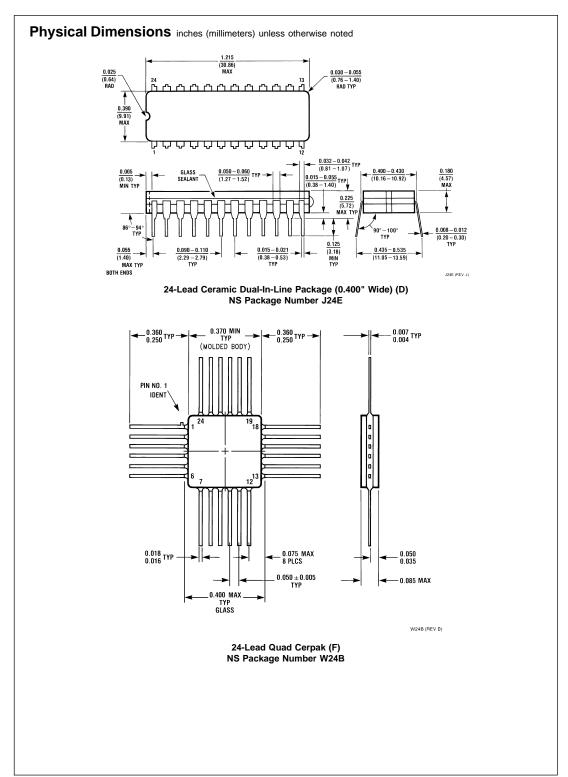

#### 24-Pin DIP

#### 24-Pin Quad Cerpak

# **Logic Diagram**

# **Truth Tables**

# **Synchronous Operation**

(Each Flip-Flop)

|                | Outputs         |                 |                 |                 |                        |

|----------------|-----------------|-----------------|-----------------|-----------------|------------------------|

| D <sub>n</sub> | CP <sub>n</sub> | CP <sub>C</sub> | MS              | MR              | Q <sub>n</sub> (t + 1) |

|                |                 |                 | SD <sub>n</sub> | CD <sub>n</sub> |                        |

| L              | ~               | L               | L               | L               | L                      |

| Н              | ~               | L               | L               | L               | Н                      |

| L              | L               | ~               | L               | L               | L                      |

| Н              | L               | ~               | L               | L               | Н                      |

| Х              | L               | L               | L               | L               | Qn(t)                  |

| X              | Н               | Х               | L               | L               | Qn(t)                  |

| Х              | Х               | Н               | L               | L               | Qn(t)                  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

U = Undefined

t = Time before CP Positive Transition

t + 1 = Time after CP Positive Transition

= LOW to HIGH Transition

# **Asynchronous Operation**

(Each Flip-Flop)

|                | Outputs         |     |                 |                 |                        |

|----------------|-----------------|-----|-----------------|-----------------|------------------------|

| D <sub>n</sub> | CP <sub>n</sub> | CPc | MS              | MR              | Q <sub>n</sub> (t + 1) |

|                |                 |     | SD <sub>n</sub> | CD <sub>n</sub> |                        |

| Х              | Х               | Х   | Н               | L               | Н                      |

| X              | Х               | Х   | L               | Н               | L                      |

| X              | X               | Х   | Н               | Н               | U                      |

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Above which the useful life may be impaired

Storage Temperature  $(T_{STG})$

-65°C to +150°C

Maximum Junction Temperature (T<sub>1</sub>)

Ceramic

+175°C

Pin Potential to

Ground Pin (V<sub>EE</sub>)

-7.0V to +0.5V

Input Voltage (DC)

Output Current

(DC Output HIGH)

ESD (Note 2)

-50 mA

V<sub>EE</sub> to +0.5V

≤ 2000V

#### **Recommended Operating Conditions**

Case Temperature (T<sub>C</sub>)

Military

-55°C to +125°C

Supply Voltage (V<sub>EE</sub>)

-5.7V to -4.2V

Note 1: Absolute maximum ratings are those values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: ESD testing conforms to MIL-STD-883, Method 3015.

# **Military Version**

### **DC Electrical Characteristics**

$V_{EE}$  = -4.2V to -5.7V,  $V_{CC}$  =  $V_{CCA}$  = GND,  $T_{C}$  = -55°C to +125°C

| Symbol           | Parameter            | Min   | Max   | Units | T <sub>c</sub> | Conditions                           |              | Notes     |

|------------------|----------------------|-------|-------|-------|----------------|--------------------------------------|--------------|-----------|

| V <sub>OH</sub>  | Output HIGH Voltage  | -1025 | -870  | mV    | 0°C to         | V <sub>IN</sub> = V <sub>IH</sub>    | Loading with | (Notes 3, |

|                  |                      |       |       |       | +125°C         | (Max)                                | 50Ω to -2.0V | 4, 5)     |

|                  |                      | -1085 | -870  | mV    | –55°C          | or V <sub>IL</sub> (Min)             |              |           |

| V <sub>OL</sub>  | Output LOW Voltage   | -1830 | -1620 | mV    | 0°C to         | 1                                    |              |           |

|                  |                      |       |       |       | +125°C         |                                      |              |           |

|                  |                      | -1830 | -1555 | mV    | –55°C          | 1                                    |              |           |

| V <sub>OHC</sub> | Output HIGH Voltage  | -1035 |       | mV    | 0°C to         | V <sub>IN</sub> = V <sub>IH</sub>    | Loading with | (Notes 3, |

|                  |                      |       |       |       | +125°C         | (Min)                                | 50Ω to -2.0V | 4, 5)     |

|                  |                      | -1085 |       | mV    | –55°C          | or V <sub>IL</sub> (Max)             |              |           |

| V <sub>OLC</sub> | Output LOW Voltage   |       | -1610 | mV    | 0°C to         | 1                                    |              |           |

|                  |                      |       |       |       | +125°C         |                                      |              |           |

|                  |                      |       | -1555 | mV    | −55°C          | 1                                    |              |           |

| V <sub>IH</sub>  | Input HIGH Voltage   | -1165 | -870  | mV    | −55°C to       | Guaranteed HIG                       | SH Signal    | (Notes 3, |

|                  |                      |       |       |       | +125°C         | for all Inputs                       |              | 4, 5, 6)  |

| V <sub>IL</sub>  | Input LOW Voltage    | -1830 | -1475 | mV    | −55°C to       | Guaranteed LOW Signal for all Inputs |              | (Notes 3, |

|                  |                      |       |       |       | +125°C         |                                      |              | 4, 5, 6)  |

| I <sub>IL</sub>  | Input LOW Current    | 0.50  |       | μA    | −55°C to       | V <sub>EE</sub> = -4.2V              |              | (Notes 3, |

|                  |                      |       |       |       | +125°C         | $V_{IN} = V_{IL} (Min)$              |              | 4, 5)     |

| I <sub>IH</sub>  | Input HIGH Current   |       | 240   | μA    | 0°C to         | V <sub>EE</sub> = -5.7V              |              | (Notes 3, |

|                  |                      |       |       |       | +125°C         | $V_{IN} = V_{IH} (Max)$              |              | 4, 5)     |

|                  |                      |       | 340   | μA    | −55°C          | 1                                    |              |           |

| I <sub>EE</sub>  | Power Supply Current | -130  | -50   | mA    | −55°C to       | Inputs Open                          |              | (Notes 3, |

|                  |                      |       |       |       | +125°C         |                                      |              | 4, 5)     |

Note 3: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55°C), then testing immediately without allowing for the junction temperature to stabilize due to heat dissipation after power-up. This provides "cold start" specs which can be considered a worst case

Note 4: Screen tested 100% on each device at  $-55^{\circ}$ C,  $+25^{\circ}$ C, and  $+125^{\circ}$ C, Subgroups, 1, 2, 3, 7 and 8.

Note 5: Sampled tested (Method 5005, Table I) on each manufactured lot at -55°C, +25°C, and +125°C, Subgroups A1, 2, 3, 7 and 8.

Note 6: Guaranteed by applying specified input condition and testing V<sub>OH</sub>/V<sub>OL</sub>.

# **AC Electrical Characteristics**

$V_{\rm EE}$  = -4.2V to -5.7V,  $V_{\rm CC}$  =  $V_{\rm CCA}$  = GND

| Symbol              | Parameter                                             | T <sub>C</sub> = -55°C |      | T <sub>C</sub> = +25°C |      | T <sub>C</sub> = +125°C |      | Units | Conditions                            | Notes        |

|---------------------|-------------------------------------------------------|------------------------|------|------------------------|------|-------------------------|------|-------|---------------------------------------|--------------|

|                     |                                                       | Min                    | Max  | Min                    | Max  | Min                     | Max  |       |                                       |              |

| f <sub>max</sub>    | Toggle Frequency                                      | 400                    |      | 400                    |      | 400                     |      | MHz   | Figures 2, 3                          | (Note<br>10) |

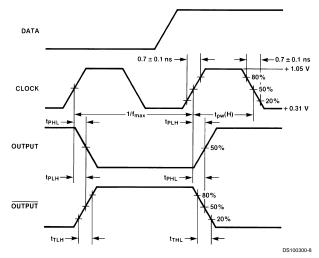

| t <sub>PLH</sub>    | Propagation Delay                                     | 0.50                   | 2.20 | 0.60                   | 2.00 | 0.50                    | 2.40 | ns    |                                       |              |

| t <sub>PHL</sub>    | CP <sub>C</sub> to Output                             |                        |      |                        |      |                         |      |       | Figures 1, 3                          |              |

| t <sub>PLH</sub>    | Propagation Delay                                     | 0.50                   | 2.20 | 0.60                   | 2.00 | 0.50                    | 2.40 | ns    |                                       |              |

| t <sub>PHL</sub>    | CP <sub>n</sub> to Output                             |                        |      |                        |      |                         |      |       |                                       |              |

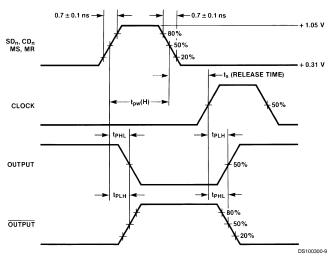

| t <sub>PLH</sub>    | Propagation Delay                                     | 0.50                   | 2.20 | 0.60                   | 2.00 | 0.50                    | 2.40 |       | $CP_n$ , $CP_C = L$ Figures           |              |

| t <sub>PHL</sub>    | CD <sub>n</sub> , SD <sub>n</sub> to Output           |                        |      |                        |      |                         |      | ns    | 1, 4                                  | 7, 8,        |

| t <sub>PLH</sub>    | ]                                                     | 0.50                   | 2.40 | 0.60                   | 2.10 | 0.50                    | 2.50 |       | CP <sub>n</sub> , CP <sub>C</sub> = H | 9)           |

| t <sub>PHL</sub>    |                                                       |                        |      |                        |      |                         |      |       |                                       |              |

| t <sub>PLH</sub>    | Propagation Delay                                     | 0.70                   | 2.70 | 0.80                   | 2.60 | 0.80                    | 2.90 |       | CP <sub>n</sub> , CP <sub>C</sub> = L |              |

| t <sub>PHL</sub>    | MS, MR to Output                                      |                        |      |                        |      |                         |      | ns    |                                       |              |

| t <sub>PLH</sub>    |                                                       | 0.70                   | 2.90 | 0.80                   | 2.80 | 0.80                    | 3.10 |       | CP <sub>n</sub> , CP <sub>C</sub> = H |              |

| t <sub>PHL</sub>    |                                                       |                        |      |                        |      |                         |      |       |                                       |              |

| t <sub>TLH</sub>    | Transition Time                                       | 0.20                   | 1.40 | 0.20                   | 1.40 | 0.20                    | 1.40 | ns    | Figures 1, 3, 4                       |              |

| t <sub>THL</sub>    | 20% to 80%, 80% to 20%                                |                        |      |                        |      |                         |      |       |                                       |              |

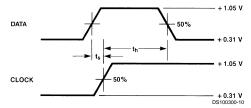

| t <sub>s</sub>      | Setup Time                                            |                        |      |                        |      |                         |      |       | Figure 5                              |              |

|                     | D <sub>n</sub>                                        | 1.00                   |      | 0.80                   |      | 0.90                    |      |       |                                       | (Note        |

|                     | CD <sub>n</sub> , SD <sub>n</sub> (Release Time)      | 1.50                   |      | 1.30                   |      | 1.60                    |      | ns    | Figure 4                              | 10)          |

|                     | MS, MR (Release Time)                                 | 2.50                   |      | 2.30                   |      | 2.50                    |      |       |                                       |              |

| t <sub>h</sub>      | Hold Time D <sub>n</sub>                              | 1.50                   |      | 1.30                   |      | 1.60                    |      | ns    | Figure 5                              |              |

| t <sub>pw</sub> (H) | Pulse Width HIGH                                      |                        |      |                        |      |                         |      |       |                                       |              |

|                     | CP <sub>n</sub> , CP <sub>C</sub> , CD <sub>n</sub> , | 2.00                   |      | 2.00                   |      | 2.00                    |      | ns    | Figures 3, 4                          |              |

|                     | SD <sub>n</sub> , MR, MS                              |                        |      |                        |      |                         |      |       |                                       |              |

Note 7: F100K 300 Series cold temperature testing is performed by temperature soaking (to guarantee junction temperature equals -55°C), then testing immediately without allowing for the junction temperature to stabilize due to heat dissipation after power-up. This provides "cold start" specs which can be considered a worst case condition at cold temperatures.

Note 8: Screen tested 100% on each device at +25  $^{\circ}\text{C}.$  Temperature only, Subgroup A9.

Note 9: Sample tested (Method 5005, Table I) on each Mfg. lot at +25°C, Subgroup A9, and at +125°C, and -55°C Temp., Subgroups A10 and A11.

Note 10: Not tested at +25°C, +125°C and -55°C Temperature (design characterization data).

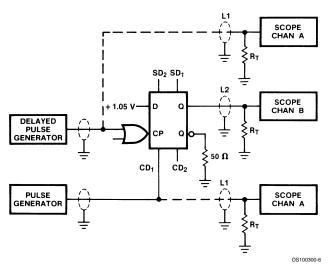

# **Test Circuits**

FIGURE 1. AC Test Circuit

# Notes:

Notes:

$$\begin{split} &V_{CC},\ V_{CCA} = +2V,\ V_{EE} = -2.5V \\ &L1\ \text{and}\ L2 = \text{Equal length }50\Omega\ \text{impedance lines} \\ &R_T = 50\Omega\ \text{terminator internal to scope} \\ &\text{Decoupling }0.1\ \mu\text{F from GND to }V_{CC}\ \text{and }V_{EE} \\ &\text{All unused outputs are loaded with }50\Omega\ \text{to GND} \\ &C_L = \text{Fixture and stray capacitance} \leq 3\ \text{pF} \end{split}$$

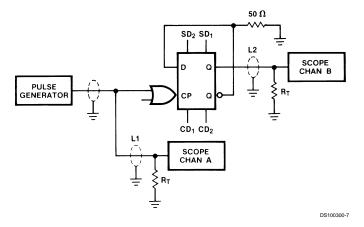

FIGURE 2. Toggle Frequency Test Circuit

# **Switching Waveforms**

FIGURE 3. Propagation Delay (Clock) and Transition Times

FIGURE 4. Propagation Delay (Resets)

FIGURE 5. Data Setup and Hold Time

Note 11:  $t_s$  is the minimum time before the transition of the clock that information must be present at the data input. Note 12:  $t_h$  is the minimum time after the transition of the clock that information must remain unchanged at the data input.

www.national.com

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMI-CONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

National Semiconductor Corporation Americas Tel: 1-800-272-9959 Fax: 1-800-737-7018 Email: support@nsc.com

www.national.com

National Semiconductor

National Semiconductor

Europe

Fax: +49 (0) 1 80-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 1 80-530 85 85

English Tel: +49 (0) 1 80-532 78 32

Français Tel: +49 (0) 1 80-532 93 58

Italiano Tel: +49 (0) 1 80-532 93 58

Asia Pacific Customer Response Group

Tel: 65-2544466

Fax: 65-2504466

Email: sea.support@nsc.com

National Semiconductor

National Semiconductor Japan Ltd.

Tel: 81-3-5620-6175

Fax: 81-3-5620-6179